Khi Huawei và Tập đoàn Quốc tế về Sản xuất chất bán dẫn Trung Quốc (SMIC) được cấp bằng sáng chế cho phương pháp quang khắc bốn mẫu hình tự căn chỉnh (SAQP) để sản xuất các vi mạch tiên tiến vào đầu năm nay, hầu hết đều cho rằng các công ty này đang nghiên cứu chế tạo chip bằng quy trình chế tạo 5nm. Tuy nhiên, kế hoạch thực sự còn đi xa hơn và Huawei hiện đang mong muốn sử dụng phương pháp trên cho công nghệ sản xuất tiến trình 3nm.

SiCarrier, một nhà phát triển thiết bị sản xuất chip được chính phủ Trung Quốc hậu thuẫn đang hợp tác với Huawei, cũng vừa được cấp bằng sáng chế cho kỹ thuật đa mẫu. Điều này xác nhận thêm kế hoạch sử dụng cả kỹ thuật này cho các chip 3nm trong tương lai.

|

| Chip SMIC bên trong điện thoại Huawei Mate 60 Pro. (Ảnh: Bloomberg) |

Các chuyên gia như Dan Hutcheson từ TechInsights cho rằng mặc dù SAQP có thể cho phép Trung Quốc sản xuất chip loại 5nm, nhưng máy quang khắc EUV vẫn sẽ rất cần thiết để phát triển xa hơn. Chuyên gia trong ngành chưa bao giờ hình dung ra việc sử dụng SAQP cho các node vi mạch lớp 3nm.

Công nghệ xử lý cấp 7nm có các metal pitch 36nm–38nm, trong khi các node 5nm thu nhỏ metal pitch xuống 30nm–32nm. Ở 3nm, metal pitch sẽ đạt khoảng 21nm–24nm. Để đạt được kích thước này, Huawei và SMIC có kế hoạch áp dụng SAQP bằng máy quang khắc DUV, công nghệ thấp hơn EUV.

SAQP rất quan trọng đối với Huawei và SMIC vì họ thiếu quyền truy cập vào các công cụ in quang khắc hàng đầu của ASML bởi lệnh cấm từ Hoa Kỳ và châu Âu. SAQP là kỹ thuật khắc nhiều lần các đường trên tấm silicon để tăng mật độ bóng bán dẫn, giảm mức tiêu thụ điện năng và nâng cao hiệu suất. Trước đây, để tránh dựa vào máy in quang khắc EUV, Intel cũng phải sử dụng kỹ thuật này trong giai đoạn 2019–2021 với node 10nm (sau này được đổi tên thành "Intel 7").

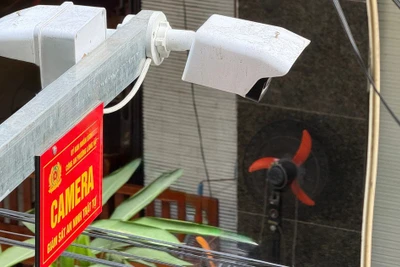

|

| SAQP là phương pháp đa mẫu kết hợp với công nghệ quang khắc cũ DUV - giải pháp đang được các nhà sản xuất Trung Quốc sử dụng khi không thể tiếp cận EUV do hạn chế từ Hà Lan đối với việc xuất khẩu máy làm chip của ASML. (Ảnh: Wikipedia) |

Bất chấp những lợi ích tiềm tàng, việc sử dụng SAQP đặt ra những thách thức khó khăn. Công nghệ xử lý lớp 10nm thế hệ đầu tiên của Intel ít nhất đã thất bại một phần do phương pháp này. Năng suất được đồn là tệ đến mức CPU Canon Lake 10nm duy nhất chỉ có hai lõi CPU và đồ họa tích hợp đã bị vô hiệu hóa. Tuy nhiên, đối với SMIC, SAQP là cần thiết để phát triển công nghệ bán dẫn, cho phép sản xuất các chip phức tạp hơn – bao gồm bộ xử lý HiSilicon Kiri thế hệ tiếp theo dành cho thiết bị tiêu dùng và bộ xử lý Ascend cho máy chủ AI.

Mặc dù chi phí cho mỗi chip 5nm hoặc 3nm sử dụng SAQP gần như chắc chắn sẽ cao hơn, khiến nó ít khả thi hơn (nếu có) đối với các thiết bị thương mại, nhưng phương pháp này vẫn rất quan trọng đối với những tiến bộ của Trung Quốc trong công nghệ bán dẫn. Những tiến bộ này rất cần thiết không chỉ cho thiết bị điện tử tiêu dùng mà còn cho các ứng dụng như siêu máy tính và khả năng phát triển năng lực quân sự.

Máy quang khắc EUV của ASML mang lại lợi ích khổng lồ cho ngành công nghiệp chip. Với bước sóng rất ngắn, chỉ 13,5nm, ngắn hơn nhiều so với bước sóng 193nm của máy quang khắc DUV, máy quang khắc EUV giải quyết hàng loạt vấn đề mà ngành công nghiệp chip đang gặp phải.

Trước khi EUV ra đời, bước sóng lớn của DUV khiến việc in quang khắc ở các tiến trình nhỏ rất khó khăn. Để in được các đường rãnh nhỏ hơn, gọi là đa mẫu hình, bắt đầu từ mẫu hình kép. Với phương pháp này, mỗi lớp mẫu hình của con chip không còn được in chỉ trong một lần như trước đây mà sẽ được chia thành hai lớp với mật độ bóng bán dẫn thấp hơn. Tiếp theo, hai lớp này sẽ trải qua hai quá trình in và khắc riêng biệt để tạo thành hai mẫu hình sơ bộ. Sau đó, các mẫu hình này sẽ được kết hợp và xếp chồng lên nhau, tạo ra một mẫu hình cuối cùng với các đường khắc mịn hơn và khoảng cách hẹp hơn trên tấm wafer.

Tuy nhiên, do cấm vận, các công ty Trung Quốc không thể tiếp cận EUV mà chỉ có thể sử dụng DUV. Để vượt qua rào cản kỹ thuật nhằm in các node nhỏ hơn, họ buộc phải sử dụng một kỹ thuật gọi là quang khắc bốn mẫu hình tự căn chỉnh (SAQP). SAQP cao cấp hơn giải pháp quang khắc mẫu hình kép, tuy nhiên hệ quả là công đoạn sản xuất sẽ rất phức tạp, kéo dài và tốn kém.